# A Fully Integrated 1.9-GHz CMOS Low-Noise Amplifier

Cheon Soo Kim, *Member, IEEE*, Min Park, *Member, IEEE*, Chung-Hwan Kim, Yeong Cheol Hyeon, Hyun Kyu Yu, *Member, IEEE*, Kwyro Lee, *Senior Member, IEEE*, and Kee Soo Nam, *Member, IEEE*

**Abstract**—A fully integrated 1.9-GHz CMOS low-noise amplifier (LNA) has been implemented in a 0.8- $\mu$ m CMOS technology. For low-noise performance, the amplifier employs high-quality spiral inductors with a quality factor of 8.5–12.5, and device layout and bias condition of the active devices were optimized for low-noise conditions. This amplifier showed a noise figure of 2.8 dB with a forward gain of 15 dB at current consumption of 15 mA. To the authors' knowledge, this represents the lowest noise figure reported to date for a fully integrated CMOS LNA operating at 1.9 GHz.

**Index Terms**—CMOS LNA, fully integrated amplifier, low noise.

## I. INTRODUCTION

THE strong demand for portable wireless communication systems motivates the research of radio frequency (RF) modules using CMOS technology. The use of CMOS technology is very attractive for the integrating the baseband intermediate frequency (IF) and RF modules in a single chip. Recently, RF receivers for 1.9 GHz have been implemented by submicron CMOS technology [1]–[5]. Since the noise performance of the fully integrated CMOS low-noise amplifier (LNA) is poor, most of the reported LNA circuits use high-quality off-chip inductors that include bonding wires to prevent any further degradation of noise performance. However, using bonding wire as an inductor has a drawback of repeatability. The noise performance of a monolithic LNA depends on the circuit topology, the minimum noise figure ( $F_{\min}$ ) of the active device, and the quality factor ( $Q$ ) of spiral inductors. The major cause of poor noise performance in fully integrated LNA's is due to the low quality of on-chip spiral inductors.

In this letter, we demonstrate a fully integrated, very low-noise 1.9-GHz CMOS LNA employing high- $Q$  inductors and optimized active devices. The measured the noise performance of the amplifier agrees well with the simulation using the parameters obtained from the active device and high- $Q$  spiral inductors.

## II. LNA DESIGN

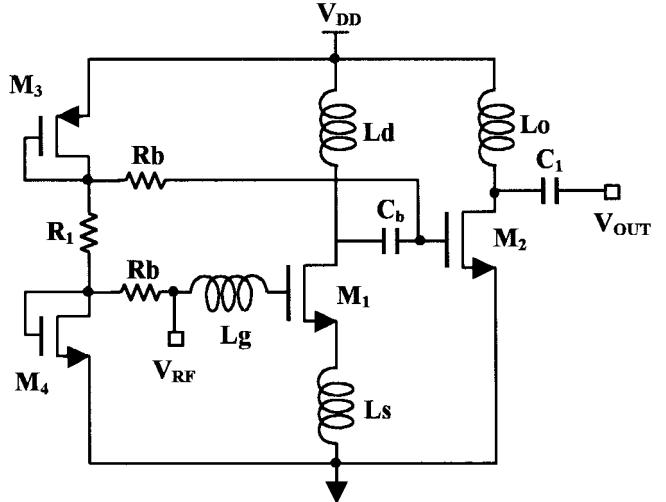

A schematic of the two-stage LNA is shown in Fig. 1. The first stage of the circuit employs a common source with

Manuscript received April 21, 1998. This work was supported by the Ministry of Informations and Communication, Korea.

C. S. Kim, M. Park, C.-H. Kim, Y. C. Hyeon, H. K. Yu, and K. S. Nam are with the Semiconductor Division, Electronics and Telecommunications Research Institute, Taejon, 305-350, Korea.

K. Lee is with the Department of Electrical Engineering, Korea Advanced Institute of Science and Technology, Taejon, 305-701, Korea.

Publisher Item Identifier S 1051-8207(98)05620-7.

Fig. 1. Simplified schematic of the fully integrated LNA.

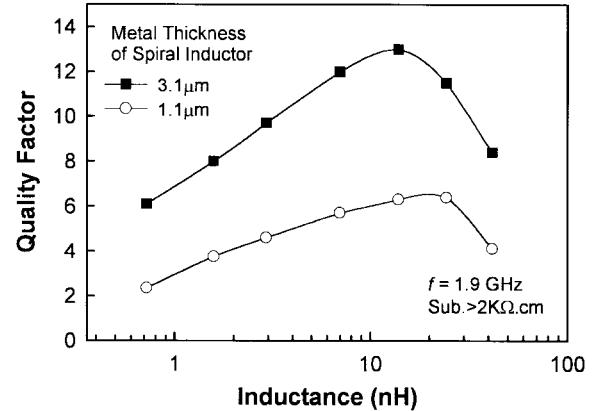

Fig. 2. Quality factor versus inductance of spiral inductors fabricated with standard (1.1  $\mu$ m) process and thick (3.1  $\mu$ m) metal process.

inductive source degeneration type for simultaneous matching of noise and power gain [3]–[5]. The transistor  $M_1$  with the channel width of 600  $\mu$ m was selected for low  $F_{\min}$  and convenience in matching [6]. Our 0.8- $\mu$ m n-MOSFET with the channel width of 600  $\mu$ m has a  $F_{\min}$  of 1.0 dB at drain current of 5 mA [6]. The bias condition of the second-stage transistor  $M_2$  was chosen for the high gain and linearity. Transistors  $M_3$  and  $M_4$  with 10-k $\Omega$  resistor  $R_b$  for ac blocking forms the biasing circuitry. The 6.8-nH inductor  $L_g$  and 9-nH inductor  $L_0$  are used for input and output matching, respectively. The inductors with a thick metal (3.1  $\mu$ m) have a  $Q$  value of 12.5 and an inductance of 9 nH as shown in Fig. 2 [7], [8].

TABLE I

COMPARISON OF 1.6–1.9-GHz CMOS LNA PERFORMANCE REPORTED IN THE LITERATURE

| Author                 | freq.   | Gain  | NF     | Current | Input Matching | Technology   | Ref. |

|------------------------|---------|-------|--------|---------|----------------|--------------|------|

| Shaeffer <i>et al.</i> | 1.6 GHz | 22 dB | 2.4 dB | 5 mA    | Wire+on chip   | 0.5 $\mu$ m  | [1]  |

| Wu <i>et al.</i>       | 1.8 GHz | 20 dB | -      | 5 mA    | Off chip       | 0.6 $\mu$ m  | [2]  |

| Shahani <i>et al.</i>  | 1.6 GHz | 17 dB | 3.8 dB | 8 mA    | On chip        | 0.35 $\mu$ m | [3]  |

| Rudel <i>et al.</i>    | 1.9 GHz | 22 dB | 5.0 dB | 12 mA   | Wire+on chip   | 0.6 $\mu$ m  | [4]  |

| Shaeffer <i>et al.</i> | 1.6 GHz | 22 dB | 3.5 dB | 20 mA   | Wire+on chip   | 0.6 $\mu$ m  | [5]  |

| <b>This work</b>       | 1.9 GHz | 15 dB | 2.8 dB | 15 mA   | On chip        | 0.8 $\mu$ m  | -    |

The LNA was simulated with linear simulator using the measured  $S$ - and noise parameter data for the active devices, and the lumped small signal equivalent circuit parameter of high- $Q$  spiral inductors.

### III. EXPERIMENTAL RESULTS

The LNA circuit was fabricated using 0.8- $\mu$ m standard CMOS technology fabricated on high-resistivity silicon substrate ( $>2$  k $\Omega$ ·cm). The second metal thickness was increased to 3.1  $\mu$ m to reduce the series resistance of spiral inductors. All the measurements were carried out using on-wafer RF probes and a HP8510C Network Analyzer. Noise parameters were also measured over the frequency range of 0.3–3 GHz using an ATN setup.

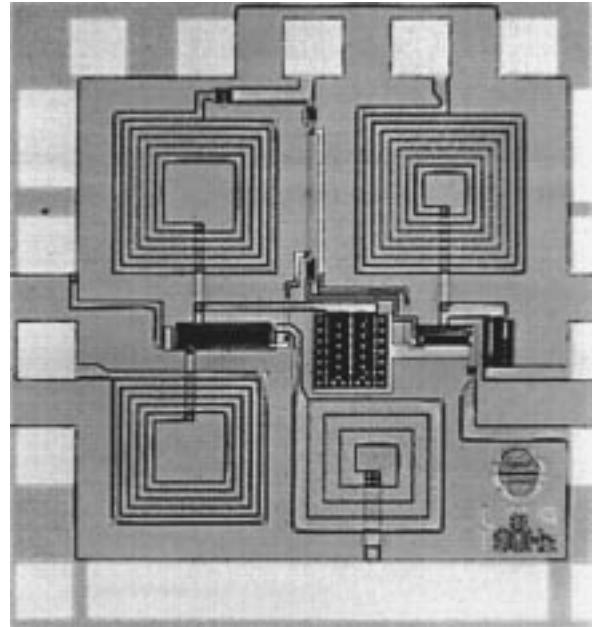

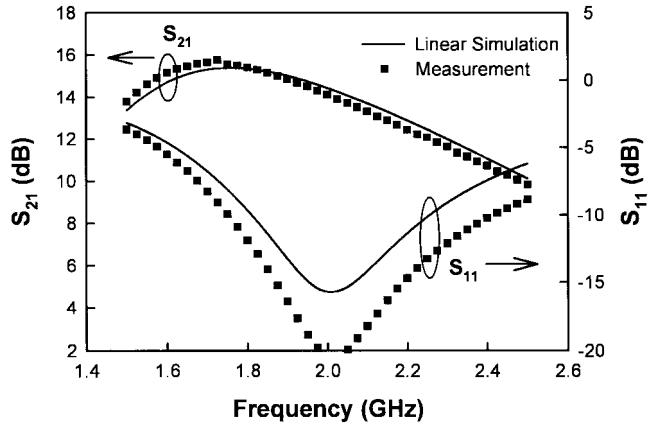

The microphotograph of a monolithic LNA fabricated using the thick metal process is shown in Fig. 3. The chip size was 0.93 mm  $\times$  0.93 mm. Fig. 4 shows the measured results of gain and  $S_{11}$  of the amplifier, which show good agreement with the simulated ones. The amplifier has a gain of 15 dB, a  $S_{11}$  of  $-16.4$  dB, and  $S_{22}$  of  $-7$  dB at 1.9 GHz. It consumes dc current of 15 mA including bias circuit from a 3.6-V supply.

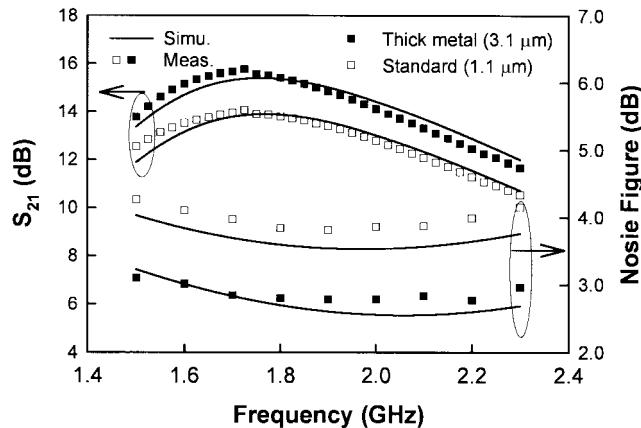

Fig. 5 compares the measured noise figure of the LNA's fabricated with standard thin- and thick-metal process. The second metal thickness of the standard and thick-metal CMOS process was 1.1 and 3.1  $\mu$ m, respectively. The circuit fabricated using thick-metal process shows the noise figure of 2.8 dB at 1.9 GHz. The performance of L-band CMOS LNA's reported in the literature is listed in Table I. Compared to other CMOS LNA's that usually use the off-chip [2], [5] or bonding wire inductor [1], [4] as input-matching element, this monolithic 1.9-GHz LNA circuit shows the lowest noise figure. Furthermore, Fig. 5 shows that an amplifier employing thick-metal inductors can improve the noise figure up to 1.0 dB and gain by 2.0 dB compared with the one fabricated with the standard thin-metal CMOS process. The noise performance of the LNA's can be expected accurately by the simulation using small-signal parameters of active and passive devices.

The amplifier has a measured  $-1$ -dB input compression point of  $-10$  dBm, and the measured third-order intermodulation intercept point was 2 dBm referred at the input.

### IV. CONCLUSIONS

A fully integrated 1.9-GHz CMOS LNA with high- $Q$  inductors has been designed and fabricated using a 0.8- $\mu$ m CMOS

Fig. 3. Microphotograph of CMOS LNA fabricated with thick metal process. The four inductors and bias circuit were also integrated in a chip that has the size of 0.93 mm  $\times$  0.93 mm.

Fig. 4. Measured versus simulated gain and  $S_{11}$  of the proposed LNA. The maximum gain peak obtained at 1.7 GHz, because the amplifier has the minimum  $S_{22}$  at 1.65 GHz with the value of  $-18$  dB.

technology on high-resistivity silicon substrate with the thick metal process. The measured noise figure and gain at a supply voltage of 3.6 V are 2.8 and 15 dB, respectively, which agrees

Fig. 5. Comparison between measured and simulated gain and the noise figure of LNA's fabricated with standard thin and thick metal process.

well with the simulation results calculated using small-signal parameters obtained separately from the active and the passive devices.

## REFERENCES

- [1] D. K. Shaeffer, A. Shahani, S. Mohan, H. Samavati, H. Rategh, M. Hershenson, M. Xu, C. Yue, D. Eddleman, and T. Lee, "A 115mW CMOS GPS receiver," in *ISSCC Dig. Tech. Papers*, Feb. 1998, pp. 122-123.

- [2] S. Wu and B. Razavi, "A 900 MHz/1.8 GHz CMOS receiver for dual band applications," in *ISSCC Dig. Tech. Papers*, Feb. 1998, pp. 122-123.

- [3] A. R. Shahani, D. K. Shaeffer, and T. H. Lee, "A 12 mW wide dynamic range CMOS front-end for a portable GPS receiver," *IEEE J. Solid-State Circuits*, vol. 32, pp. 2061-2070, Dec. 1997.

- [4] J. C. Rudell, J. J. Ou, T. B. Cho, G. Chien, F. Brianti, J. A. Weldon, and P. R. Gray, "A 1.9 GHz wide-band IF double conversion CMOS integrated receiver for codress telephone applications," in *ISSCC Dig. Tech. Papers*, Feb. 1997, pp. 304-305.

- [5] D. K. Shaeffer and T. H. Lee, "A 1.5V, 1.5 GHz CMOS low noise amplifier," in *Symp. VLSI Circuit Dig. Tech. Papers*, 1996, pp. 32-33.

- [6] C. S. Kim, H. K. Yu, H. Cho, S. Lee, and K. S. Nam, "CMOS layout and bias optimization for RF IC design applications," in *IEEE MTT-S Microwave Symp. Dig.*, 1997, pp. 945-948.

- [7] M. Park, C. S. Kim, J. M. Park, H. K. Yu, and K. S. Nam, "High Q microwave inductors in CMOS double-metal technology and its substrate bias effects for 2 GHz RF IC's application," in *IEDM Tech. Dig.*, 1997, pp. 59-62.

- [8] M. Park, S. Lee, H. K. Yu, and K. S. Nam, "Optimization of high Q CMOS-compatible microwave inductors using silicon CMOS technology," in *IEEE MTT-S Microwave Symp. Dig.*, 1997, pp. 129-132.